# **Preliminary Program**

|              | 2016/10/26 Wednesday Day 1 (1/3)                                                   |                               |

|--------------|------------------------------------------------------------------------------------|-------------------------------|

|              | Tutorials (No. 5 Meeting Room)                                                     |                               |

| 9:30 – 10:30 | Jin Jang Kyung Hee University, Korea                                               |                               |

|              | "Device and Process Technologies of Oxide and LTPS TFTs for Display Manufacturing" |                               |

| 10:30 –      | Arokia Nathan University of Cambridge, UK                                          |                               |

| 11:30        | "Oxide Semiconductor TFT Technology for Circuits and Systems"                      |                               |

|              | Lunch                                                                              | Registration (09:00 – 18:00)  |

| 13:30 –      | Tse Nga (Tina) Ng University of California San Diego, USA                          | 110gistiation (03.00 – 10.00) |

| 14:30        | "Printed Organic TFT Sensor Tags"                                                  |                               |

| 14:30 -      | Feng Yan The Hong Kong Polytechnic University, China                               |                               |

| 15:30        | "Biosensors based on Thin Film Transistors"                                        |                               |

| 15:30 -      | Break                                                                              |                               |

| 16:00        |                                                                                    |                               |

| 16:00 –      | Panel Discussion organized by IEEE EDS Organic Electronics Committee               |                               |

| 18:00        | "Opportunities and Challenges of Organic Thin-Film Transistors"                    |                               |

|                          | 2016/10/27 Thւ                                                                                                                                 | ırsday Day 2             | 0 (2/3)                                                                                                                                                                               |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08:45 –<br>09:00         | Opening (Gingko Hall,银杏大厅)                                                                                                                     | nsday bay z              | - (213)                                                                                                                                                                               |

| 09:00 –<br>10:30         | Plenary Session 1 (Gingko Hall,银杏大厅)                                                                                                           |                          |                                                                                                                                                                                       |

| 09:00 - 09:30            | Samar Saha President of IEEE Electron Dev<br>"IEEE Electron Devices Society: Mission and Technical Ac                                          | •                        |                                                                                                                                                                                       |

| 09:30 - 10:00            | Arokia Nathan University of Cambridge, UK "Design Tools for TFT Circuits and Systems"                                                          |                          |                                                                                                                                                                                       |

| 10:00 - 10:30            | <b>Kwang-Ting (Tim) Cheng</b> Hong Kong University of So "Robust Design and Reliability Simulation for TFT Circuits"                           |                          | nology, China                                                                                                                                                                         |

|                          | Coff                                                                                                                                           | ee Break                 |                                                                                                                                                                                       |

| 10:50 –                  | Session 1: Devices and Circuits for Displays                                                                                                   | 10:50 –                  | Session 2: High Performance TFTs (No. 5 Meeting Room)                                                                                                                                 |

| 12:15                    | (Gingko Hall)                                                                                                                                  | 12:15                    |                                                                                                                                                                                       |

| 10:50 – 11:10<br>Invited | Yanzhao Li BOE, China "TFT Recent Progress and Its Applications"                                                                               | 10:50 – 11:10<br>Invited | Lei Liao Wuhan University, China  "Rational Hydrogenation for Enhanced Mobility and High Reliability on ZnO-based Thin Film Transistors: from Simulation to Experiment"               |

| 11:10 – 11:30<br>Invited | Lei Wang Guangzhou New Vision Optoelectronic Tech., China  "Progress on Flexible & Printed OLED Displays and their TFT Backplane Technology"   | 11:10 – 11:30<br>Invited | Yong-Young Noh  Dongguk University, Korea  "Development of High Performance Printed Ambipolar Polymer and Carbon Nanotube Complementary Integrated Circuits for Flexible Electronics" |

| 11:30 – 11:45            | Siming Hu Kunshan New Flat Panel Display Tech. Center,<br>China "A New CMOS Pixel Compensation Circuit for AMOLED Display"                     | 11:30 – 11:45            | Shubin Pi Fudan University, China Investigation of Nitrogen Doping and Double Channel Layers for the Indium Tungsten Oxide Thin Film Transistors                                      |

| 11:45 – 12:00            | Wenjiang Liu Shanghai Jiao Tong University, China "Current Feedback Driving with Dynamic Supply Voltage Scaling for Low Power AMOLED Displays" | 11:45 – 12:00            | Changdong Chen Sun Yat-Sen University, China "Ultra-High Mobility Thin-film Transistors with MOCVD Growth In <sub>2</sub> O <sub>3</sub> "                                            |

| 12:00 –                  | Linlin Fang Northeastern University,                                                                                                           | 12:00 – 12:15            | Seungpyo Hong Kyung Hee University, Korea                                                                                                                                             |

| 12:15                | China                                                            |               | "Reduction of Leakage Current by Wet Annealing on BLA Polycrystalline   |

|----------------------|------------------------------------------------------------------|---------------|-------------------------------------------------------------------------|

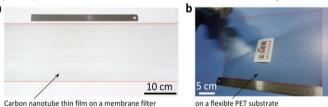

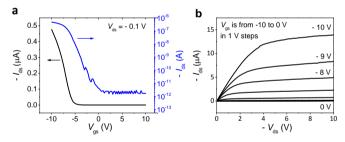

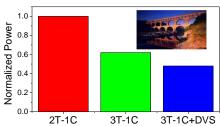

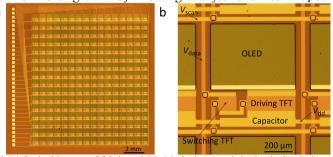

|                      | "Carbon Nanotube Thin-film Transistors and Driving Circuits for  |               | Silicon Thin-Film Transistor"                                           |

|                      | Flexible Display Application"                                    |               |                                                                         |

|                      |                                                                  | _unch         |                                                                         |

| 14:00 -              | Session 3: TFT New Applications (Gingko Hall)                    | 14:00 –       | Session 4: Printed TFTs (No. 5 Meeting Room)                            |

| 15:10                |                                                                  | 15:10         | , , ,                                                                   |

| 14:00 14:20          | Qing Wan Nanjing University, China                               | 14:00 14:20   | Mario Caironi CNST of IIT, Italy                                        |

| 14:00 – 14:20        | "Oxide-based Electric-Double-Layer Thin-Film Transistors For     | 14:00 – 14:20 | "Enhancing the Speed of Printed and Direct-written Polymer Transistors" |

| Invited              | Neuromorphic Systems"                                            | Invited       |                                                                         |

| 14:20 – 14:40        | Kai Wang Sun Yat-Sen University, China                           | 14:20 – 14:40 | Linfeng Lan South China University of Technology, China                 |

| Invited              | "Beyond Display: Emerging Applications of Thin-Film Transistors" | Invited       | "Printed Short-channel Thin-film Transistors"                           |

|                      | Vahid Keshmiri Linköping University, Sweden                      |               | Jianwen Zhao SINANO, CAS, China                                         |

| 14:40 – 14:55        | The Applications of OECTs in Supercapacitor Balancing Circuits"  | 14:40 – 14:55 | "Printed Thin-film Transistors and Circuits Based on Sorted             |

|                      |                                                                  |               | Semiconducting Single-walled Carbon Nanotubes"                          |

|                      | Hantao He Sun Yat-sen University, China                          |               | Guixia Jiang Qingdao University, China                                  |

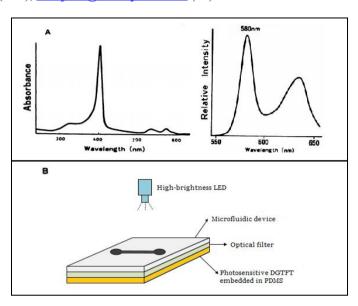

| 14:55 – 15:10        | "A Fluorescence Detector for Rapid On-Chip Detection of Amniotic | 44.55 45.40   | "Solution-Processed High-k Magnesium Oxide Dielectric for n-Type        |

| 14.55 – 15.10        | Fluid Embolism Biomarker Based on Dual-Gate Photosensitive       | 14:55 – 15:10 | In <sub>2</sub> O <sub>3</sub> and p-Type NiO Thin Film Transistors"    |

|                      | Thin-Film Transistor"                                            |               |                                                                         |

|                      | Coff                                                             | ee Break      |                                                                         |

| 15:30 –              | Session 5: TCAD and Compact Modeling (Gingko                     | 15:30 –       | Session 6: Device Stabilities (No. 5 Meeting Room)                      |

| 16:55                | Hall)                                                            | 16:55         |                                                                         |

| 15:30 – 15:50        | Ahmed Nejim Silvaco, UK                                          | 15:30 – 15:50 | Shengdong Zhang Peking University, China                                |

| Invited              | "TCAD for Compact Model Development? Get Real!"                  | Invited       | "Oxygen Adsorption Effects of Metal Oxide Thin Film Transistors"        |

| 15:50 <b>–</b> 16:10 | Radu Sporea University of Surrey, UK                             | 15:50 – 16:10 | Hongtao Cao NIMTE, CAS, China                                           |

|                      | "TCAD and Circuit Simulation of Thermal Effects in Source-gated  |               | "Investigation on the Stability of Ambipolar SnO TFTs"                  |

| Invited              | Transistors"                                                     | Invited       |                                                                         |

|                      | Quan Chen The University of Hong Kong, China                     |               | Wei Tang Shanghai Jiao Tong University, China                           |

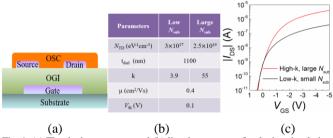

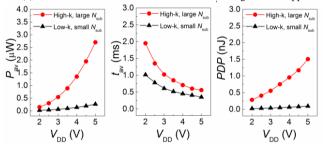

| 16:10 – 16:25        | "Artificial Neural Network Compact Model for TFTs"               | 16:10 – 16:25 | "Improved Bias Stress Stability for Low-voltage Polymer OTFTs with      |

|                      |                                                                  |               | Low-k/High-k Bilayer Gate Dielectric"                                   |

| 16:25 – 16:40        | Guangwei Xu Institute of Microelectronics, CAS, China            | 16:25 – 16:40 | Gongtan Li Sun Yat-Sen University, China                                |

|               | "The Description of Pinch-off Point for Short Channel Organic Thin |               | "Nitrogen Doping Amorphous InGaZnO Thin Film Transistors for Highl |  |

|---------------|--------------------------------------------------------------------|---------------|--------------------------------------------------------------------|--|

|               | Film Transistors"                                                  |               | Stable Operation Under Gate Bias and Light Stressing"              |  |

|               | Jielin Fang Jinan University, China                                |               | Jianeng Xu Shanghai Jiao Tong University, China                    |  |

| 16:40 – 16:55 | "Physical Modeling of AOS TFTs Based on Symmetric Quadrature       | 16:40 – 16:55 | "Ambient Effects on the Light Illumination Stability of Amorphous  |  |

|               | Method Considering Degenerate Regime"                              |               | InGaZnO Thin Film Transistors"                                     |  |

|               |                                                                    |               |                                                                    |  |

| 17:00-18:30   | Poster Session (Gingko Hall)                                       |               |                                                                    |  |

| 18:40         | Banquet                                                            |               |                                                                    |  |

|               | 2016/10/28 Friday Day 3 (3/3)                                   |                    |                                                                                      |  |  |

|---------------|-----------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------|--|--|

| 9:00 - 10:30  | 30 Plenary Session 2 (Gingko Hall)                              |                    |                                                                                      |  |  |

| 00:00 00:20   | Benjamin Iñiguez, Universitat Rovirai Virgili, Spain            |                    |                                                                                      |  |  |

| 09:00 - 09:30 | "Recent Progress in TFT Compact Modeling and Parame             | ter Extraction Te  | chniques"                                                                            |  |  |

| 00:20 40:00   | Yunqi Liu Institute of Chemistry, Chinese Academy of S          | Sciences, China    |                                                                                      |  |  |

| 09:30 - 10:00 | "High Performance Organic Field-Effect Transistors and 0        | Circuits"          |                                                                                      |  |  |

| 10:00 - 10:30 | Jamal Deen McMaster University, Canada                          |                    |                                                                                      |  |  |

| 10.00 - 10.30 | "Compact Modeling of Organic/Polymeric Thin Film Trans          | istors - Past, Pre | esent and Future"                                                                    |  |  |

|               | Coff                                                            | fee Break          |                                                                                      |  |  |

| 10:50 – 12:15 | Session 7: Circuit Design (Gingko Hall)                         | 10:50 –            | Session 8: Simulation & Characterization (No. 5 Meeting                              |  |  |

| 10.50 - 12.15 |                                                                 | 12:20              | Room)                                                                                |  |  |

|               | Jordi Carrabina Bordoll Univ Autonoma de Barcelona,             |                    | Chao Jiang The National Center for Nanoscience and Tech.,                            |  |  |

| 10:50 – 11:10 | Spain                                                           | 10:50 – 11:10      | China                                                                                |  |  |

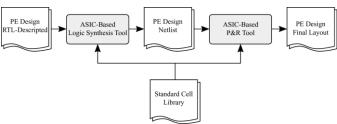

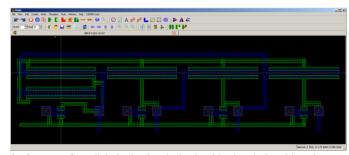

| Invited       | "Process Design Kit and EDA Tools for Organic/Printed           | Invited            | "Vertical Charge Transport via Small Polaron Hopping within Lamellar                 |  |  |

|               | Electronics"                                                    |                    | Organic Single Crystal"                                                              |  |  |

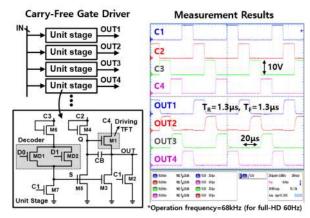

| 11:10 – 11:30 | Byong-Deok Choi Hanyang University, Korea                       | 11:10 – 11:30      | Sungsik Lee University of Cambridge, UK                                              |  |  |

| Invited       | "Oxide-TFT Circuit Design for High-Reliability Flexible         | Invited            | "Threshold Voltage and Conduction Mechanisms in Disordered                           |  |  |

| IIIVILEG      | Electronics"                                                    | mvitea             | Semiconductor-based Thin Film Transistors"                                           |  |  |

| 11:30 – 11:45 | Qinghang Zhao Tsinghua University, China,                       | 11:30 – 11:50      | <b>Di Geng</b> Kyung Hee University, Korea                                           |  |  |

| 11.50 – 11.40 | "Noise Margin Analysis for Pseudo-CMOS Circuits"                | Invited            | "Mobility and V <sub>th</sub> Extraction by Time-of-flight Analysis for a-IGZO TFTs" |  |  |

|               | Manuel Llamas Universitat Autònoma de Barcelona,                |                    | Zhiheng Han Institute of Microelectronics, CAS, China                                |  |  |

| 11:45 – 12:00 | Spain                                                           | 11:50 – 12:05      | "Surface Potential Measurement on Contact Resistance of a-IGZO TFTs                  |  |  |

| 11.40 12.00   | "Technology Independent Yield-Aware Place & Route Strategy      | 11.00 12.00        | by Kelvin Probe Force Microscopy"                                                    |  |  |

|               | for Printed Electronics Gate Array Circuits"                    |                    |                                                                                      |  |  |

|               | Huimin Li Sun Yat-sen University, China                         |                    | Michiaki Sakamoto Japan Display Inc., Japan                                          |  |  |

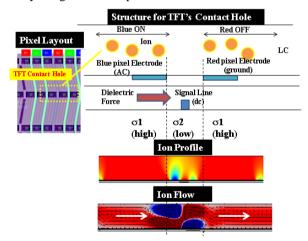

| 12:00 – 12:15 | "Design Methodology for a Fingerprint Sensor-Integrated Display | 12:05 – 12:20      | "Simulation for Unidirectional Ion Flow in TFT-LCDs Induced by                       |  |  |

|               | Pixel and Array based on Dual-Gate a-Si:H Photosensitive TFT"   |                    | AC-Pixel-Driving Signals"                                                            |  |  |

|               |                                                                 | _unch              |                                                                                      |  |  |

| 14:00 – 15:10 | Session 9: New Material TFTs (Gingko Hall)                      | 14:00 –            | Session 10: Organic TFTs (No. 5 Meeting Room)                                        |  |  |

|                          |                                                                                                                                                                           | 15:10                    |                                                                                                                                                                              |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14:00 – 14:20<br>Invited | Xuelei Liang Peking University, China "Carbon Nanotube Thin Film Transistors for Display Technology"                                                                      | 14:00 – 14:20<br>Invited | Simon Ogier Neudrive, UK  "High Performance Flexible OTFT Materials and Processes for Display, Logic and Sensor Applications"                                                |

| 14:20 – 14:40<br>Invited | <b>Fukai Shan</b> Qingdao University, China "The Fully Solution-processed p-type Metal Oxide Thin Film and its Integration for Thin Film Transistors"                     | 14:20 – 14:40<br>Invited | Chuan Liu Sun Yat-sen University, China "On the Controversy of Carrier Mobility in Organic TFTs"                                                                             |

| 14:40 – 14:55            | Yuzhi Li South China University of Technology, China "Low Temperature, Stable Thin-film Transistors based on Photo-patternable Solution-processed InOx:Li Semiconductors" | 14:40 – 14:55            | Longzhen Qiu Hefei University of Technology, China "Polymer Brush Modified Surface for High-performance Inkjet-printed Organic Thin-film Transistors"                        |

| 14:55 – 15:10            | Lingyan Liang NIMTE, CAS, China "The Physical Properties of Zn-Sn-N Thin Films and their TFT Application"                                                                 | 14:55 – 15:10            | Jiaqing Zhao Shanghai Jiao Tong University, China "Low Voltage Organic Thin-film Transistor with Reduced Sub-gap DOS for Power Efficient Logic Circuits"                     |

|                          | Coff                                                                                                                                                                      | ee Break                 |                                                                                                                                                                              |

| 15:30-16:55              | Session 11: New Circuit Technologies (Gingko Hall)                                                                                                                        | 15:30-16:55              | Session 12: Flexible TFTs (No. 5 Meeting Room)                                                                                                                               |

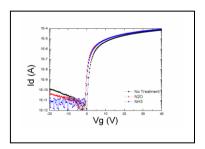

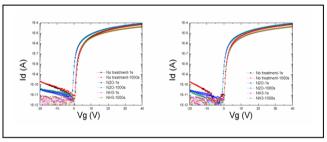

| 15:30 – 15:50<br>Invited | Ta-Ya Chu National Research Council, Canada "Development of Printed Logic Circuits"                                                                                       | 15:30 – 15:50<br>Invited | Xifeng Li Shanghai University, China High Stability of Low Temperature and Flexible IGZO TFT by Plasma Treatment                                                             |

| 15:50 – 16:10<br>Invited | <b>Deyu Tu</b> Linköping University, Sweden  "Organic Power Electronics: AC-DC Conversion with  High-Voltage Organic Thin-film Transistors"                               | 15:50 – 16:10<br>Invited | Dong-Ming Sun Institute of Metal Research, CAS, China  "Scale-up Fabrication of Single Wall carbon Nanotube Thin Film and its Application in Flexible Thin-film Transistors" |

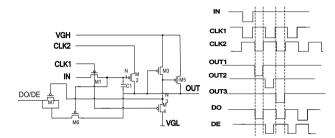

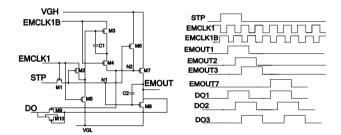

| 16:10 – 16:25            | Nan Yang Kunshan New Flat Panel Display Tech Center,<br>China "A New p-type Shift Register with Detection Function for<br>Flexible Display"                               | 16:10 – 16:25            | Kun Hu Kunshan New Flat Panel Display Tech Center, China  "Failure Mechanism of TFT Devices on Flexible Substrate by Cyclic Bending Test"                                    |

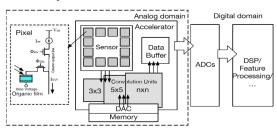

| 16:25 – 16:40            | <b>Zheyu Liu</b> Tsinghua University, Beijing, China "Computable Flexible Electronics: Circuits Exploring for Image                                                       | 16:25 – 16:40            | Younwoo Choe Kyung Hee University, Korea "Bendable Corbino a-IGZO TFTs"                                                                                                      |

|                               | Filtering Accelerator with OTFT"                                                                                                             |  |                                                                                                                                                       |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------------------------------------------------------------------------------------------------------------------------------------------|

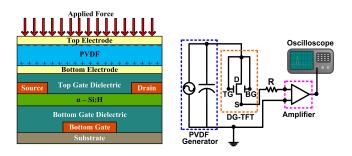

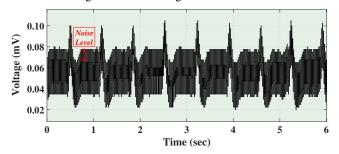

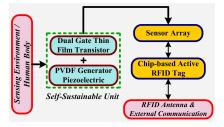

| 16:40 – 16:55                 | Ahmed Rasheed Sun Yat-Sen University, China  "Heart Rate/Impulse Monitoring Using Autonomous PVDF-Integrated Dual-Gate Thin-Film Transistor" |  | Peng Xiao South China University of Technology, China  "High-mobility Flexible Thin-film Transistors with Zirconium-doped Indium Oxide Channel Layer" |

| 17:10-17:40<br>( Gingko Hall) | Award Session Announcement of 2018 CAD-TFT Closing remarks                                                                                   |  | ,                                                                                                                                                     |

#### **Abstract for Tutorials**

| No. | Title                                                                            | Author            | Affiliation                                |

|-----|----------------------------------------------------------------------------------|-------------------|--------------------------------------------|

| T01 | Device and Process Technologies of Oxide and LTPS TFTs for Display Manufacturing | Jin Jang          | Kyung Hee University, Korea                |

| T02 | Oxide Semiconductor TFT Technology for Circuits and Systems                      | Arokia Nathan     | University of Cambridge, UK                |

| Т03 | Printed Organic TFT Sensor Tags                                                  | Tse Nga (Tina) Ng | University of California San Diego,<br>USA |

| T04 | Biosensors based on Thin Film Transistors                                        | Feng Yan          | Hong Kong Polytechnic University, China    |

## **Abstract for Plenary Presentations**

| No.  | Title                                                               | Author            | Affiliation                          |

|------|---------------------------------------------------------------------|-------------------|--------------------------------------|

| PI01 | IEEE Electron Devices Society: Mission and Technical Activities     | Samar Saha        | President of IEEE Electron Device    |

| FIUI | TEEE Electron Devices Society. Mission and Technical Activities     | Salliai Salia     | Society                              |

| PI02 | Design Tools for TFT Circuits and Systems                           | Arokia Nathan     | University of Cambridge, UK          |

| PI03 | Robust Design and Reliability Simulation for TFT Circuits           | Kwang-Ting (Tim)  | Hong Kong University of Science and  |

| F103 |                                                                     | Cheng             | Technology, China                    |

| PI04 | Recent Progress in TFT Compact Modeling and Parameter Extraction    | Benjamin Iñiguez  | Universitat Rovirai Virgili, Spain   |

| F104 | Techniques                                                          | Denjaniin iniguez | Offiversitat Noviral Virgili, Spaili |

| PI05 | High Performance Organic Field-Effect Transistors and Circuits      | Yungi Liu         | Institute of Chemistry, Chinese      |

| F103 | right Fehormance Organic Field-Effect Transistors and Circuits      | runqi Liu         | Academy of Sciences, China           |

| PI06 | Compact Modeling of Organic/Polymeric Thin Film Transistors - Past, | M. Jamal Deen     | McMaster University, Canada          |

| F100 | Present and Future                                                  | ivi. Jamai Deen   | iviciviastei Offiversity, Callada    |

#### **Abstract for Invited Presentations**

| No.    | Title                                                                                                                                    | Topic                             | Author            | Affiliation                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------|--------------------------------------------------------|

| INV1-1 | TFT Recent Progress and Its Applications                                                                                                 |                                   | Yanzhao Li        | BOE, China                                             |

| INV1-2 | Progress on Flexible & Printed OLED Displays and their TFT Backplane Technology                                                          | Devices and Circuits for Displays | Lei Wang          | Guangzhou New Vision<br>Optoelectronic Tech.,<br>China |

|        |                                                                                                                                          |                                   |                   |                                                        |

| INV2-1 | Rational Hydrogenation for Enhanced Mobility and High Reliability on ZnO-based Thin Film Transistors: from Simulation to Experiment      | High Performance TFTs             | Lei Liao          | Wuhan University, China                                |

| INV2-2 | Development of High Performance Printed Ambipolar Polymer and Carbon Nanotube Complementary Integrated Circuits for Flexible Electronics |                                   | Yong-Young<br>Noh | Dongguk University,<br>Korea                           |

|        |                                                                                                                                          |                                   |                   |                                                        |

| INV3-1 | Oxide-based Electric-Double-Layer Thin-Film Transistors For Neuromorphic Systems           | TFT New Applications          | Qing Wan                   | Nanjing University, China                        |

|--------|--------------------------------------------------------------------------------------------|-------------------------------|----------------------------|--------------------------------------------------|

| INV3-2 | Beyond Display: Emerging Applications of Thin-Film Transistors                             |                               | Kai Wang                   | Sun Yat-Sen University,<br>China                 |

|        |                                                                                            |                               |                            |                                                  |

| INV4-1 | Enhancing the Speed of Printed and Direct-written Polymer Transistors                      | D I TET.                      | Mario Caironi              | CNST of IIT, Italy                               |

| INV4-2 | Printed Short-channel Thin-film Transistors                                                | Printed TFTs                  | Linfeng Lan                | South China University of Technology, China      |

|        |                                                                                            |                               |                            |                                                  |

| INV5-1 | TCAD for Compact Model Development? Get Real!                                              | TOAD and Comment              | Ahmed Nejim                | Silvaco, UK                                      |

| INV5-2 | TCAD and Circuit Simulation of Thermal Effects in Source-gated Transistors                 | TCAD and Compact  Modeling    | Radu Sporea                | University of Surrey, UK                         |

| INV6-1 | Oxygen Adsorption Effects of Metal Oxide Thin Film Transistors                             | Device Stabilities            | Shengdong<br>Zhang         | Peking University, China                         |

| INV6-2 | Investigation on the Stability of Ambipolar SnO TFTs                                       |                               | Hongtao Cao                | NIMTE, CAS, China                                |

|        |                                                                                            |                               |                            |                                                  |

| INV7-1 | Process Design Kit and EDA Tools for Organic/Printed Electronics                           | Circuit Decima                | Jordi Carrabina<br>Bordoll | Univ Autonoma de<br>Barcelona, Spain             |

| INV7-2 | Oxide-TFT Circuit Design for High-Reliability Flexible Electronics                         | Circuit Design                | Byong-Deok<br>Choi         | Hanyang University,<br>Korea                     |

|        | ,                                                                                          |                               |                            |                                                  |

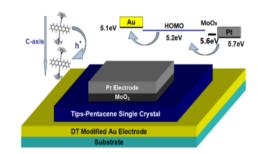

| INV8-1 | Vertical Charge Transport via Small Polaron Hopping within Lamellar Organic Single Crystal | Simulation & Characterization | Chao Jiang                 | National Center for Nanoscience and Tech., China |

| INV8-2  | Threshold Voltage and Conduction Mechanisms in Disordered Semiconductor-based Thin Film Transistors                 |                             | Sungsik Lee      | University of Cambridge,<br>UK                         |

|---------|---------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|--------------------------------------------------------|

| INV8-3  | Mobility and V <sub>th</sub> Extraction by Time-of-flight Analysis for a-IGZO TFTs                                  |                             | Di Geng          | Kyung Hee University,<br>Korea                         |

| INV9-1  | Carbon Nanotube Thin Film Transistors for Display Technology                                                        |                             | Xuelei Liang     | Peking University, China                               |

| INV9-2  | The Fully Solution-processed p-type Metal Oxide Thin Film and its Integration for Thin Film Transistors             | New Material TFTs           | Fukai Shan       | Qingdao University, China                              |

| INV10-1 | High Performance Flexible OTFT Materials and Processes for Display, Logic and Sensor Applications                   | Organic TFTs                | Simon Ogier      | NeuDrive Limited, Biohub, Macclesfield, United Kingdom |

| INV10-2 | On the Controversy of Carrier Mobility in Organic TFTs                                                              |                             | Chuan Liu        | Sun Yat-sen University,<br>China                       |

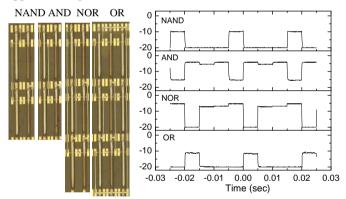

| INV11-1 | Development of Printed Logic Circuits                                                                               | New Circuit<br>Technologies | Ta-Ya Chu        | National Research<br>Council, Canada                   |

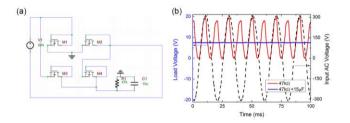

| INV11-2 | Organic Power Electronics: AC-DC Conversion with High-Voltage Organic Thin-film Transistors                         |                             | Deyu Tu          | Linköping University,<br>Sweden                        |

|         |                                                                                                                     |                             |                  |                                                        |

| INV12-1 | High Stability of Low Temperature and Flexible IGZO TFT by Plasma Treatment                                         | Flexible TFTs               | Xifeng Li        | Shanghai University,<br>China                          |

| INV12-2 | Scale-up Fabrication of Single Wall carbon Nanotube Thin Film and its Application in Flexible Thin-film Transistors |                             | Dong-Ming<br>Sun | Institute of Metal<br>Research, CAS, China             |

#### **Abstract for Oral Presentations**

| No.   | Title                                                                                                                                                 | Topic                    | Author            | Affiliation                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------|-----------------------------------------|

| 01-01 | Withdrawn                                                                                                                                             |                          |                   |                                         |

| O1-02 | Current Feedback Driving with Dynamic Supply Voltage Scaling for Low Power AMOLED Displays                                                            | Devices and Circuits for | Wenjiang Liu      | Shanghai Jiao Tong<br>University, China |

| O1-03 | Carbon Nanotube Thin-film Transistors and Driving Circuits for Flexible Display Application                                                           | Displays                 | Linlin Fang       | Northeastern University,<br>China       |

|       |                                                                                                                                                       |                          |                   |                                         |

| O2-01 | Investigation of Nitrogen Doping and Double Channel Layers for the Indium Tungsten Oxide Thin Film Transistors                                        | High Performance TFTs    | Shubin Pi         | Fudan University, China                 |

| O2-02 | Ultra-High Mobility Thin-film Transistors with MOCVD Growth In <sub>2</sub> O <sub>3</sub>                                                            |                          | Yanli Pei         | Sun Yat-Sen University ,<br>China       |

| O2-03 | Reduction of Leakage Current by Wet Annealing on BLA Polycrystalline Silicon Thin-Film Transistor                                                     |                          | Seungpyo<br>Hong  | Kyung Hee University,<br>Korea          |

|       |                                                                                                                                                       |                          |                   |                                         |

| O3-01 | The Applications of OECTs in Supercapacitor Balancing Circuits                                                                                        | TFT New Applications     | Vahid<br>Keshmiri | Linköping University,<br>Sweden         |

| O3-02 | A Fluorescence Detector for Rapid On-Chip Detection of<br>Amniotic Fluid Embolism Biomarker Based on Dual-Gate<br>Photosensitive Thin-Film Transistor |                          | Hantao He         | Sun Yat-sen University,<br>China        |

| 04-01 | Printed Thin-film Transistors and Circuits Based on Sorted Semiconducting Single-walled Carbon Nanotubes                            | Printed TFTs               | Jianwen Zhao     | SINANO, CAS, China                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|----------------------------------------------|

| O4-02 | Solution-Processed High-k Magnesium Oxide Dielectric for n-Type In <sub>2</sub> O <sub>3</sub> and p-Type NiO Thin Film Transistors | Fillited 1F15              | Guixia Jiang     | Qingdao University, China                    |

|       |                                                                                                                                     |                            |                  |                                              |

| O5-01 | Artificial Neural Network Compact Model for TFTs                                                                                    | TCAD and Compact  Modeling | Quan Chen        | The University of Hong<br>Kong, China        |

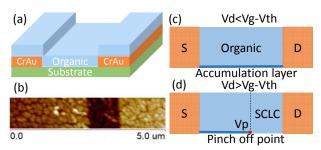

| O5-02 | The Description of Pinch-off Point for Short Channel Organic Thin Film Transistors                                                  |                            | Guangwei Xu      | Institute of Microelectronics,<br>CAS, China |

| O5-03 | Physical Modeling of AOS TFTs Based on Symmetric Quadrature Method Considering Degenerate Regime                                    |                            | Jielin Fang      | Jinan University, China                      |

|       |                                                                                                                                     |                            |                  |                                              |

| O6-01 | Improved Bias Stress Stability for Low-voltage Polymer OTFTs with Low-k/High-k Bilayer Gate Dielectric                              | Device Stabilities         | Wei Tang         | Shanghai Jiao Tong<br>University, China      |

| O6-02 | Nitrogen Doping Amorphous InGaZnO Thin Film Transistors for Highly Stable Operation Under Gate Bias and Light Stressing             |                            | Gongtan Li       | Sun Yat-Sen University,<br>China             |

| O6-03 | Ambient Effects on the Light Illumination Stability of Amorphous InGaZnO Thin Film Transistors                                      |                            | Jianeng Xu       | Shanghai Jiao Tong<br>University, China      |

|       |                                                                                                                                     |                            |                  |                                              |

| 07-01 | Noise Margin Analysis for Pseudo-CMOS Circuits                                                                                      | Circuit Design             | Qinghang<br>Zhao | Tsinghua University, China,                  |

| 07-02 | Technology Independent Yield-Aware Place & Route Strategy for Printed Electronics Gate Array Circuits                               |                            | Manuel<br>Llamas | Universitat Autònoma de<br>Barcelona, Spain  |

| O7-03 | Design Methodology for a Fingerprint Sensor-Integrated Display Pixel and Array based on Dual-Gate a-Si:H                            |                            | Huimin Li        | Sun Yat-sen University,<br>China             |

|        | Photosensitive TFT                                                             |                                  |                 |                                |

|--------|--------------------------------------------------------------------------------|----------------------------------|-----------------|--------------------------------|

|        |                                                                                |                                  |                 |                                |

| O8-01  | Surface Potential Measurement on Contact Resistance of                         | Simulation &<br>Characterization | Zhiheng Han     | Institute of Microelectronics, |

|        | a-IGZO TFTs by Kelvin Probe Force Microscopy                                   |                                  | NAC - L C - L C | CAS, China                     |

| O8-02  | Simulation for Unidirectional Ion Flow in TFT-LCDs Induced                     |                                  | Michiaki        | Japan Display Inc., Japan      |

|        | by AC-Pixel-Driving Signals                                                    |                                  | Sakamoto        |                                |

|        | Low Temperature, Stable Thin-film Transistors based on                         |                                  | V 1:1:          | South China University of      |

| O9-01  | O9-01 Photo-patternable Solution-processed InOx:Li Semiconductors New Material | New Material TFTs                | Yuzhi Li        | Technology, China              |

| O9-02  | The Physical Properties of Zn-Sn-N Thin Films and their TFT                    |                                  | Lingyan Liang   | NIMTE, CAS, China              |

| 09-02  | Application                                                                    |                                  | Lingyan Liang   | MINITE, OAG, Officia           |

|        |                                                                                |                                  | <del>,</del>    | <del>,</del>                   |

| O10-01 | Polymer Brush Modified Surface for High-performance                            | Organic TFTs                     | Longzhen Qiu    | Hefei University of            |

| 01001  | Inkjet-printed Organic Thin-film Transistors                                   |                                  | Longzhon wa     | Technology, China              |

| O10-02 | Low Voltage Organic Thin-film Transistor with Reduced                          |                                  | Jiaqing Zhao    | Shanghai Jiao Tong             |

| 010 02 | Sub-gap DOS for Power Efficient Logic Circuits                                 |                                  | Jiaqirig Zriao  | University, China              |

|        |                                                                                |                                  | T               |                                |

| O11-01 | A New p-type Shift Register with Detection Function for                        | New Circuit Technologies         | Nan Yang        | Kunshan New Flat Panel         |

| 011 01 | Flexible Display                                                               |                                  | - Nan rang      | Display Tech Center, China     |

| O11-02 | Computable Flexible Electronics: Circuits Exploring for Image                  |                                  | Zheyu Liu       | Tsinghua University,           |

| 011-02 | Filtering Accelerator with OTFT                                                |                                  | Zileya Lia      | Beijing, China                 |

| O11-03 | Heart Rate/Impulse Monitoring Using Autonomous                                 |                                  | Ahmed           | Sun Yat-Sen University,        |

|        | PVDF-Integrated Dual-Gate Thin-Film Transistor                                 |                                  | Rasheed         | China                          |

|        |                                                                                |                                  |                 | <u> </u>                       |

| O12-01 | Failure Mechanism of TFT Devices on Flexible Substrate by                      | Flexible TFTs                    | Kun Hu          | Kunshan New Flat Panel         |

|        | Cyclic Bending Test                               |           | Display Tech Center, Cl |

|--------|---------------------------------------------------|-----------|-------------------------|

| O12-02 | Bendable Corbino a-IGZO TFTs                      | Younwoo   | Kyung Hee University    |

|        |                                                   | Choe      | Korea                   |

| O12-03 | High-mobility Flexible Thin-film Transistors with | Dong Vice | South China University  |

|        | Zirconium-doped Indium Oxide Channel Layer        | Peng Xiao | Technology, China       |

### **Abstract for Poster Presentations**

| No.  | Title                                                                                                                     | Author       | Affiliation                                 |

|------|---------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------|

| P001 | Organic-inorganic Hybrid Ambipolar Field-effect Transistor with a Cytop interlayer                                        | Sheng Sun    | South China University of Technology, China |

| P002 | Contact Length Optimization in Organic Thin-Film Transistors                                                              | Shiwei Wu    | Xidian University, China                    |

| P003 | Charge trapping performance based in Zr0.5Hf0.5O2 for nonvolatile memory                                                  | Xiaobing Yan | Hebei University, China                     |

| P004 | A Physical Model for Double Gate Amorphous InGaZnO Thin Film Transistors Based on Multiple Trapping and Release Mechanism | Guanhua Yang | Institute of Microelectronics, CAS, China   |

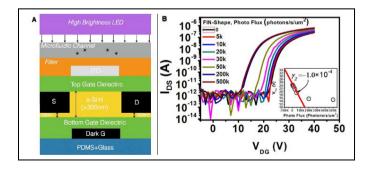

| P005 | Three-Dimensional Fin-Shape Dual-Gate Photosenstive a-Si:H Thin-Film Transistor for Low Dose X-Ray Imaging                | Hai Ou       | Sun Yat-sen University, China               |

| P006 | Subthreshold Operation of PVDF-Integrated Dual-Gate Thin-Film Transistor for Tactice Sensing                              | Weiwei Li    | Sun Yat-sen University, China               |

| P007 | Low voltage organic TFTs based on higk-k/low-k dielectrics                                                                | Qiutan Ke    | Sun Yat-sen University, China               |

| P008 | Solution Combustion Synthesis of Alumina Gate Dielectric using Hydrogen Peroxide/Water Solvent                            | Bo Liu       | Sun Yat-sen University, China               |

| P009 | Effects of active layer thickness and annealing temperature of                                                            | Jin Cheng    | Beijing Institute of Technology,            |

|      | solution-processed InMgZnO thin film transistors                                                                                   |                        | China                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------|

| P010 | Laser annealing effects on the performance of InTiZnO thin film transistors                                                        | You Meng               | Qingdao University, China                                         |

| P011 | Low-temperature, Nontoxic water-induced high-k zirconium oxide dielectric for fully-solution processed oxide thin-film transistors | Chundan Zhu            | Qingdao University, China                                         |

| P012 | Solution-Processed Organic Field-effect Transistors with High Mobility and Excellent Uniformity                                    | Yukun Huang            | Shanghai Jiao Tong University,<br>China                           |

| P013 | a-IGZO Thin Film Transistors with Offset Structure for Field Emitter Array Application                                             | Xiaojie Li             | Sun Yat-sen University, China                                     |

| P014 | Simulation and study of Double-Material Gate TFT in order to reduce sub-threshold swing                                            | Atefeh<br>Rahmaninejad | Shahid Rajaee Teacher Training<br>University, iran                |

| P015 | Temperature Dependent Gate Bias Stress Effect in Dioctylbenzothieno[2,3-b]benzothiophene (C8BTBT) Based Thin Film Transistor       | Jiawei Wang            | National Center for Nanoscience and Technology, China             |

| P016 | Field-effect Electroluminescence Spectra of Reverse-biased PN Junctions in Silicon TFT Device for Microdisplay                     | Zhengfei Ma            | niversity of Electronic Science<br>and Technology of China, China |

| P017 | Flexible Thin-film Transistors Fabricated on Plastic Substrate at Low Temperature                                                  | Huijin Li              | Peking University,China                                           |

| P018 | Hybrid-Phase Microstructure in InSnZnO Thin Film and Its Application to High-Performance TFT                                       | Rongsheng Chen         | South China University of Technology, China                       |

| P019 | Flexible Transparent Field-Effect Diodes Fabricated at Low-Temperature with All Oxide Materials                                    | Yonghui Zhang          | Institute of Physics, CAS, China                                  |

| P020 | A Novel Three-Terminal UV PD on Barrier-Modulated Triple-Layer Architecture                                                        | Daqian Ye              | Institute of Physics, CAS, China                                  |

# Device and Process Technologies of Oxide and LTPS TFTs for Display Manufacturing

#### Jin Jang

Department of Information Display and Advanced Display Research Center Kyung Hee University, Seoul, Korea jjang@khu.ac.kr

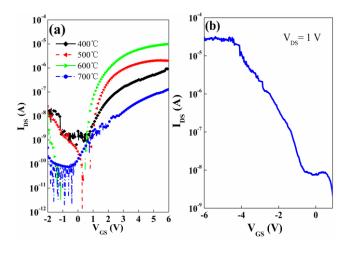

Abstract— I will review the device structure, process and performance of LTPS and oxide TFTs. Excimer laser annealing of a-Si and TFT structure for LTPS TFTs will be discussed to understand AMOLED backplane design. The device structure and performance of oxide TFTs will be also explained to understand the conditions for high performance oxide TFT with excellent stability. In addition the bulk accumulation oxide TFTs studied in our lab will be discussed together with oxide TFTs on plastic substrate.

Keywords—Oxide TFT, LTPS TFT, Bulk accumulation, TFT circuits

#### I. INTRODUCTION

P-channel LTPS TFTs are being used for manufacturing of AMOLED for smart phones and a-IGZO TFT are for AMOLED TV. Excimer laser annealing of a-Si is widely used for LTPS on glass and PI substrates with grain size of less than 400nm. Multi-shots over 10 are used to improve the quality of grains and the uniformity of grain size. On the other hand, back-channel etched (BCE) and coplanar a-IGZO TFTs are used for LCD and OLED backplanes respectively. The performance and stability of a-IGZO TFTs will be explained on the basis of device physics and material properties.

#### II. OXIDE TFTS

#### A. Device structures

Etch stopper, back-channel etched (BCE), coplanar and dual gate structure are being studied for oxide TFTs. I will discuss the issues for these structure in term of stability and high drain currents. ES TFT can be used for high quality oxide semiconductor in TFT, BCE for less mask oxide TFT process and coplanar is for high speed circuits. However, the process issues for these TFTs are very different.

#### B. High perofrmance a-IGZO TFTs with excellent stability

Bulk accumulation can be possible when the carrier concentration is almost uniformly distributed in the channel region including front and back interface regions. This is especially important because the mobility in oxide semiconductor increases with carrier concentration. We demonstrated the advantages of BA a-IGZO TFTs such as 3 to 5 times of drain currents, excellent Vth uniformity and excellent bias stability [1-9]. The device physics under the BA TFTs will be explained. Coplanar oxide TFTs will be also discussed because of its advantage of low parasitic capacitance and thus high speed gate drivers. The TFT circuits such as ring oscillator and shift resistor will be touched.

We developed non-detach technology of plastic TFTs using CNT/GO buffer layer [10] and also TFTs on neutral plane to have rollable TFTs at the radius of 0.26mm [11].

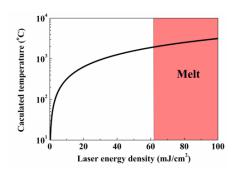

#### III. LTPS

LTPS is used for high resolution displays such as smart phone AMLCD with FFS mode and for AMOLED with top emission. Recently flexible AMOLED is a hot issue because of recent display product trend of mobile applications. I will review the conventional ELA process and issues for ELA TFTs. The device structures for AMOLED will be also explained. In order to reduce the production cost we are studying blue laser annealing of a-Si to replace current ELA LTPS [12]. The field-effect mobility of >100cm²/Vs was achieved.

#### ACKNOWLEDGMENT

This work was supported by the MOTIE (Ministry of Trade, Industry & Energy (10052044) and KDRC (Korea Display Research Corporation) support program for the development of future devices technology for display.

#### REFERENCES

- [1] M. J. Seok, M. H. Choi, M. Mativenga, D. Geng, D. Y. Kim, and J. Jang, "A fullswing a-IGZO TFT-based inverter with a top-gate-bias-induced depletion load," IEEE Electron Device Letters Vol.32, No.8, pp.1089– 1091, 2011.

- [2] M. Mativenga, S. An, and J. Jang, "Bulk accumulation a-IGZO TFT for high current and turn-on voltage uniformity," IEEE Electron Device Lett., Vol.34, No.12, pp.1533–1535, 2013.

- [3] S. Hong, S. Lee, M. Mativenga, and J. Jang, "Reduction of negative bias and light instability of a-IGZO TFTs by dual-gate driving," IEEE Electron Device Letters Vol.35, No.1, pp.93–95, 2014.

- [4] S. Lee, M. Mativenga, and J. Jang, "Removal of negative-biasillumination-stress instability in amorphous-InGaZnO thin-film transistors by top-gate offset structure," IEEE Electron Device Letters Vol.35, No.9, pp.930–932, 2014.

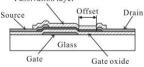

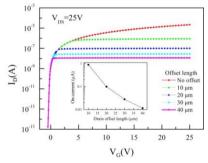

- [5] X. Li, D. Geng, M. Mativenga, and J. Jang, "High-speed dual-gate a-IGZO TFT-based circuits with top-gate offset structure," IEEE Electron Device Letters Vol.35, No.4, pp.461–463,2014.

- [6] X. Li, D. Geng, M. Mativenga, Y. Chen, and J. Jang, "Effect of bulk-accumulation on switching speed of dual-gate a-IGZO TFT based circuits," IEEE Electron Device Letters Vol.35, No.12, pp.1242–1244, 2014.

- [7] S. Lee, X. Li, M. Mativenga, J. Jang, "Bulk-Accumulation Oxide Thin-Film Transistor Circuits With Zero Gate-to-Drain Overlap Capacitance for High Speed," IEEE Electron Dev. Lett., Vol.36, No.12, pp.1329-1331, 2015.

- [8] Y. Chen, D. Geng, M. Mativenga, H. Nam, and J. Jang, "High-speed pseudo-CMOS circuits using bulk accumulation a-IGZO TFTs," IEEE Electron Device Letters Vol.36, No.2, pp.153–155, 2015.

- [9] D. Geng, Y. F. Chen, M. Mativenga, and J. Jang, "30-µm-Pitch Oxide-TFT-Based Gate-Driver Design for Small-Size, High-Resolution, and Narrow-Bezel Displays," IEEE Electron Device Letters Vol.36, No.8, pp. 805–807, 2015.G. Eason, B. Noble, and I.N. Sneddon, "On certain integrals of Lipschitz-Hankel type involving products of Bessel functions," Phil. Trans. Roy. Soc. London, vol. A247, pp. 529-551, 1955.

- [10] M. Mativenga, D. Geng, B. Kim, and J. Jang., "Fully transparent and rollable electronics" ACS Appl. Mater. Inter., Vol.7, No.3, pp.1578-1585, 2014.

- [11] Y. Kim, E. Lee, J. Um, M. Mativenga and J. Jang, "Highly Robust Neutral Plane Oxide TFTs Withstanding 0.25 mm Bending Radius for Stretchable Electronics" Scientific Reports, Vol. 6, pp. 25734, 2016.

- [12] S. Jin, Y. Choe, S. Lee, T. Kim, M. Mativenga, and J. Jang, "Lateral Grain Growth of Amorphous Silicon Films With Wide Thickness Range by Blue Laser Annealing and Application to High Performance Poly-Si TFTs," IEEE Electron Dev. Lett., Vol.37, No.3, pp.291-294, 2016.

# Oxide Semiconductor TFT Technology for Circuits and Systems

Arokia Nathan

Department of Engineering, Electrical Engineering Division

Cambridge University, Cambridge CB3 0DL, UK

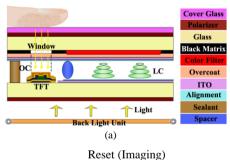

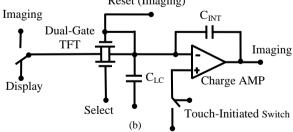

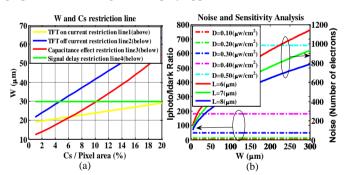

Oxide semiconductors are known for their optical transparency and high electron mobility even when processed at room temperature, making them a promising candidate for the next-generation thin film transistor (TFT) technology. Compared to existing well-established TFT technologies, the oxide transistor shows superiority in terms of process simplicity and cost, and stable device behaviour in the dark. While its non-uniformity over large areas is comparable to that of thin film silicon transistors, its photo-instability at low wavelengths can be an issue due to persistence in photoconductivity. This tutorial will review the mechanisms underlying light sensitivity in oxide transistors. Although this class of materials is optically transparent, the presence of oxygen deficiency defects, such as vacancies and interstitials located at gap states, gives rise to absorption of blue and green photons due to their ionization. In particular, the oxygen defects remain ionized even after illuminating, leading to persistent photoconductivity (PPC). This can limit the frame-rate of pixelated arrays for imaging and displays. However, despite material weaknesses, considerable progress has been made in designing oxide-based large area flat panel systems.

In this tutorial, we will address the design approaches employed for operationally stable pixel circuits for flat panel imagers and organic light emitting diode (OLED) displays. It will discuss the development of oxide TFTs for displays, including interactivity and present a contrasting study with LTPS backplanes from the standpoint of system design and compensation techniques for V<sub>T</sub> instability and OLED degradation. Besides pixel circuits and display systems, TFT-based analog and digital circuitry for signal processing and wireless power transmission are required for realization of heterogeneously integrated systems that can be realized using a combination of oxide and other technological routes on disposable/recyclable substrates. Such systems place great demand for expedient CAD tools to accurately and to reliably predict system behaviour. We review physically based CAD models, taking into account the relative dominance of the carrier transport mechanisms in the TFT, along with circuit examples.

#### **References:**

- [1] R. Chaji and A. Nathan, Thin Film Transistor Circuits and Systems, Cambridge University Press, 2013.

- [2] S. Lee, S. Jeon, R. Chaji, A. Nathan, "Transparent semiconducting oxide technology for touch free interactive displays," Proceedings of the IEEE, vol. 103, No. 4, pp. 644-664, 2015

- [3] S. Jeon, S.-E. Ahn, I. Song, C. J. Kim, U-I. Chung, E. Lee, I. Yoo, A. Nathan, S. Lee, J. Robertson, K. Kim, "Gated three-terminal device architecture to eliminate persistent photoconductivity in oxide semiconductor photosensor arrays," Nature Materials, Vol.11, No.4, pp. 301-305, Feb. 2012.

- [4] R. Chaji and A. Nathan, AMOLED panel design considerations for LTPS and MOx backplanes, SID Display Week, 2014.

## Printed organic TFT sensor tags

Tse Nga Tina Ng

Dept. of Electrical and Computer Engineering University of California San Diego La Jolla, CA 92093-0407, USA tinang@ucsd.edu

Abstract—Integrated OTFT circuits for sensor tags were implemented by all-additive solution processes. We took processing steps that improve the reliability of the fabrication process. The effect of device variations on the yield was evaluated, to account for the constraints of existing OTFT processes.

#### Keywords—inkjet printing, organic thin film transistors

Digital, additive printing of electronic materials allows rapid, highly customizable fabrication, and low-cost printed electronics are compelling for internet-of-things applications that require large volume of distributed devices, such as in sensor networks and smart packaging. With the recent improvements in solution electronic inks, it is now possible to build independent sensor systems out of printed thin-film devices. In this tutorial I will discuss the design rules we learned in the course of developing the fully printed sensor platform.

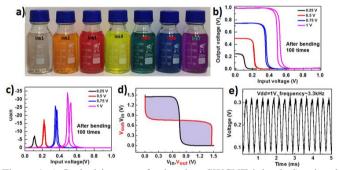

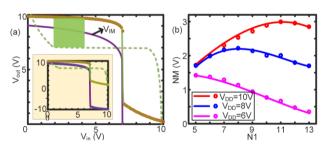

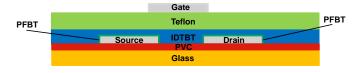

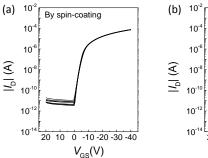

One of the prototypes (Fig. 1) is a temperature sensor tag [1] consisted of a printed thermistor bridge, a threshold control circuit, and non-volatile memories. The threshold control circuit is based on inkjet printed complementary transistors, and the non-volatile memories are capacitors with ferroelectric polymer dielectric. When the thermistor temperature exceeds a pre-set threshold (above 35°C or below 8°C), the control circuit is triggered to generate a pulse to write into the memory. This temperature sensor tag is self-contained and will be applicable to packaging or environmental monitoring applications.

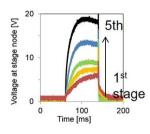

Fig. 1. OTFT temperature sensor tag (left). Pulsed voltage multiplier (right).

In electronic systems, components often require different supply voltage for operation. In order to meet this requirement and to optimize power consumption for flexible electronics, a pulsed voltage multiplier [2] is implemented to boost the voltage at specific circuit nodes above the supply voltage. A five-stage pulsed voltage multiplier is shown to provide an output voltage up to 18 V from a supply voltage of 10 V, with minimum 10 ms pulse rise time for a 70 pF load. The printed multiplier allows a single power source to deliver multiple voltage levels and enables integration of lower voltage logic with components that require higher operating voltage, for example, in the case of recording data into memory cells in sensor tags.

Lastly, a readout circuit based on a single-OTFT gain stage is demonstrated for reading ferroelectric (FE) nonvolatile rewritable memories. It was observed that high gain is not required for the readout circuit, due to the large difference in polarization charge between FE memory states. The circuit uses few OTFTs, which leads to higher yield, and does not require matching.

In addition to demonstrating the circuit performance, I will discuss some approaches to tackle the challenges of device variations and stability in printed devices [3], to improve the reliability of the fabrication processes and accelerate the development of printed electronics.

#### ACKNOWLEDGMENT

The author is grateful to her colleagues D. Schwartz, P. Mei, S. Ready, G. Whiting, J. Veres, and R. A Street at Palo Alto Research Center and Thin Film Electronics for funding the sensor tag development.

#### REFERENCES

[1] Ng, T. N.; Schwartz, D. E.; Mei, P.; Krusor, B.; Kor, S.; Veres, J.; Bröms, P.; Eriksson, T.; Wang, Y.; Hagel, O.; *et al.* Printed Dose-Recording Tag Based on Organic Complementary Circuits and Ferroelectric Nonvolatile Memories. *Sci. Rep.* **2015**, *5*, 13457.

[2] Ng, T. N.; Schwartz, D. E.; Mei, P.; Kor, S.; Veres, J.; Bröms, P.; Christer, K. Pulsed Voltage Multiplier Based on Printed Organic Devices. *Flex. Printed Electronics.* **2016**, *1*, 015002.

[3] Street, R. A.; Ng, T. N.; Schwartz, D. E.; Whiting, G. L.; Lu, J. P.; Bringans, R. D.; Veres, J. *Proc. IEEE* (2015) 103, 607.

## Biosensors Based on Thin Film Transistors

Feng Yan

Department of Applied Physics The Hong Kong Polytechnic University Hong Kong, China apafyan@polyu.edu.hk

Abstract— Thin film transistors have shown promising applications as sensors due to their high sensitivity, small size and the feasibility for multiplexing, in which solution-gated transistors are excellent potentiometric transducers for biosensors. Solution-gated transistors normal have no gate dielectric and the gate voltages are applied directly on the solid/electrolyte interfaces or electric double layers near the channel and the gate, which lead to very low working voltages (about 1 V) of the transistors. On the other hand, the devices can be easily prepared by solution process or other convenient methods because of the much simpler device structure compared with that of a conventional field effect transistor with several layers. Many biosensors can be developed based on the detection of potential changes across solid/electrolyte interfaces induced by electrochemical reactions or interactions. The devices normally show high sensitivity due to the inherent amplification function of the transistors. In this talk, I will introduce several types of biosensors studied by our group recently, including DNA, glucose, dopamine, uric acid, cell, and bacteria sensors, based on solutiongated organic electrochemical transistors and graphene transistors. The biosensors show high sensitivity and selectivity

when the devices are modified with functional nano-materials (e.g. graphene, Pt nanoparticles) and biomaterials (e.g. enzyme, antibody, DNA) on the gate electrodes or the channel. Furthermore, the devices are miniaturized successfully for the applications as sensing arrays. It is expected that the solution-gated organic transistors will find more important applications in the future.

Keywords—thin film transistor; biosensor; organic semiconductor; graphene

#### ACKNOWLEDGMENT

This work is financially supported by the Research Grants Council (RGC) of Hong Kong, China (project number: C5015-15G).

#### **Electron Devices Society: Mission and Technical Activities**

Samar K. Saha

President, IEEE Electron Devices Society

Abstract—The IEEE Electron Devices Society (EDS) is a volunteer-led and volunteer-driven dynamic Society. The mission of EDS is to promote excellence in the field of electron devices for the benefit of humanity. For over 60 years this mission has been achieved through volunteer involvement and dedication. At EDS, we realize our mission in many ways: conferences, publishing, education, and technical recognition. The EDS activities include all electron and ion based devices, in their classical or quantum states, using environments and materials in their lowest to highest conducting phase, in simple or engineered assembly, interacting with and delivering photo-electronic, electro-magnetic, electromechanical, electro-thermal, and bio-electronic signals. The Society sponsors and reports on education, research, development and manufacturing aspects and is involved in science, theory, engineering, experimentation, simulation, modeling, design, fabrication, interconnection, reliability of such devices and their applications. Also, EDS provides its members with critical resources, community-building opportunities, and support not available through any other organization or society.

The EDS has been a proud cosponsor of the CADTFT conference since its inception in 2008 at Cambridge, UK where it has been held as a workshop on *Compact Thin-Film Transistor Modeling for Circuit Simulation*. This workshop has transformed into CADTFT conference to offer display communities a forum to present and discuss all aspects of TFT Technology, modeling, and design. Attend this session to learn how EDS is evolving to meet the changing needs of the electron devices technical community, to discover how members can get more involved in the life and work of the Society, and to share your thoughts, insights, and feedback with EDS's volunteer leaders and staff. In this talk, the EDS technical activities and opportunities offered to its general membership will be discussed.

## Design Tools for TFT Circuits and Systems\*

Arokia Nathan, Xiang Cheng, Sungsik Lee, Guangyu Yao Department of Engineering, Electrical Engineering Division Cambridge University, Cambridge CB3 0DL, UK

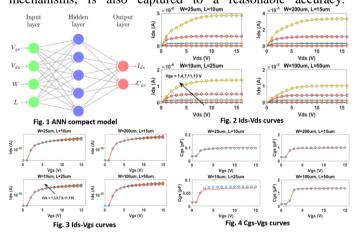

Abstract— This talk will review major developments in thin film transistor modeling for computer-aided design of circuits and systems. Based on the progress made in recent years, we have successfully developed a Verilog-AMS model called the CAMCAS model, which supports the computer-aided-design and simulation of oxide-TFTs, with the potential to be extended into other types of TFT technology families.

Keywords—compact models, oxide TFTs, SPICE, Verilog

#### I. INTRODUCTION

The growing maturity of thin film transistor (TFT) technology coupled with newly emerging materials and processes are enabling integration of circuits and systems for a new generation of applications. The design of systems places great demand for fast simulation tools to accurately and reliably predict system behavior.

Significant effort has been invested in modeling of TFTs for various semiconductor technologies, starting with amorphous silicon, and then to polysilicon, organics and recently metal oxides (see [1] and references therein). In particular, several TFTs SPICE models have been developed. Specifically the model developed by Rensselaer Polytechnic Institute, also known as the RPI model, has become a commercial standard supported by many simulation platforms including SmartSpice, HSPICE, Spectre, etc. However, no CAD tool for organic and metal-oxide TFTs has yet to become a standard. This is due to the performance improvements in materials and device structures, which makes model synthesis a dynamic process.

#### II. PHYSICALLY-BASED MODELING APPROACH

Our efforts have primarily evolved around physically-based approaches so that the models developed are simple and accurate with a minimum number of fitting parameters. The most well-studied material for TFTs is amorphous silicon. Here several models have been developed based on different distributions of deep states and tail states of the semiconductor to describe static and dynamic behavior for the above and subthreshold regimes, including other properties such as trap related  $V_T$ -shift and the off current. Without doubt, the RPI model captures most of the device properties leading to satisfactory simulation results, and thus has been widely used.

Models for organic transistors are based on multiple trapping and release (also referred to as trap-limited conduction) as well as variable range hopping. However, the underlying physics used in the model can differ due to the diverse use of materials in the TFT, ranging from gate insulation and semiconductor layer to source/drain metallization and passivation. Therefore a trend has emerged in which the efforts are to develop a unified but less physical model.

As for metal oxide TFTs, modeling efforts are still in their infancy, although there is growing interests in the area for implementation of circuits and systems. In what follows, early efforts in compact models for CAD of oxide TFTs are reviewed.

#### III. THE CAMBRIDGE TFT MODEL

Compared with amorphous silicon TFTs, the properties of the oxide materials system are unique and have to be captured. For example, localized traps or band tail states in oxides do not exist to the same extent as amorphous silicon. Their tail state density is much lower and hence trap-limited conduction is generally not as significant as in the amorphous silicon TFT. In addition, more complex systems such as amorphous indium gallium zinc oxide (a-IGZO) can have compositional disorder due to random distribution of metal constituents. This gives rise to potential barriers above the conduction band minima leading to percolation conduction [14], [16], [24].

In the presentation, we will present compact models for the terminal current-voltage behavior taking into account the different transport mechanisms in the device for the aboveand sub-threshold regimes of TFT operation. The former is based on a mobility model that combines trap-limited conduction with percolation conduction. The sub-threshold regime takes into account diffusion and drift current components. Based on this, a unified model will be presented that covers both regimes described by a single expression that uses a reference voltage  $V_{EB}$  rather than  $V_{T}$ . Good agreement with measured terminal characteristics is obtained over the entire range of  $V_{GS} > V_{FB}$  for the test TFTs with an a-IGZO channel. We will compare the differences between Verilog-AMS and SPICE from the standpoint of compact device modeling, and present the implementation of the Cambridge TFT compact model for oxide TFTs in Verilog-AMS for Spectre simulation.

#### REFERENCE

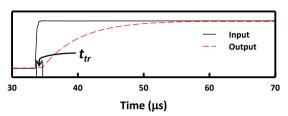

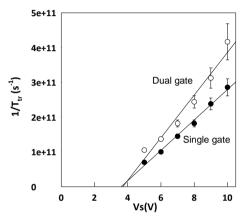

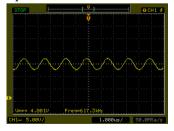

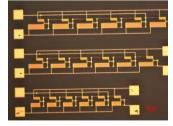

Xiang Cheng, Sungsik Lee, Guangyu Yao, Arokia Nathan, "TFT Compact Modeling," IEEE/OSA JDT, vol. 12, No. 9, pp. 898-906, 2016.